# The Analysis and Design of a Resonant Capacitively-Isolated Cockcroft-Walton Converter

Elizabeth Rabenold, Raiphy Jerez, and Samantha Coday

Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology

Email: {rabenold, coday}@mit.edu

Abstract—Capacitive isolation is a potential alternative to magnetics-based isolation in emerging applications, such as in partial power processing converter topologies, and in applications where weight and component volume are limiting factors. This work presents a capacitively-isolated Cockcroft-Walton converter capable of isolation through the flying capacitors. Generalized equations for mid-range flying capacitor voltages and switch voltages for converters of even level count are detailed. Experimental results validate the topology and analysis with a hardware prototype demonstrating 120 V input, 93.87% efficiency, and up to 60 V of isolation.

#### I. Introduction

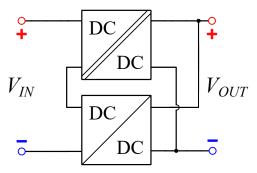

Hybrid switched-capacitor converters have been shown to be competitive with traditional magnetics-based converters in both efficiency and passive component volume due to their utilization of energy-dense capacitors for energy processing [1]. However, one important feature that is yet underdeveloped in hybrid switched-capacitor converters is isolation between the input and output voltages. Traditional implementations of galvanic isolation employ transformers to create the isolation barrier. It is important to note, though, that transformers are costly in both component volume and weight. In applications where passive volume is a key design constraint, such as in data centers and in electric aircraft, the dielectric material of capacitors may instead be used to achieve isolation [2] [3]. While typical capacitors do not offer the same safety or reliability as magnetic isolation, capacitor-based isolation can still be utilized in alternative applications, such as in enabling partial power processing or in composite converters. This work is motivated by converter applications that require extreme conversion ratios and output regulation. In such applications, series-input, parallel-output stacked converters can achieve high power density [4] [5] [6], though such topologies require isolation to allow for a series-input configuration. An example system architecture for a series-input parallel-output composite converter is shown in Fig. 1. Previous work introduced a capacitively-isolated Dickson converter [7] [8], which utilizes capacitors for energy processing and as the isolation barrier for a composite converter, thereby enabling the high conversion ratios required for tethered robots in space [9]. Existing literature [10] demonstrates the viability of the Cockcroft-Walton converter for extreme conversion ratios. This work proposes the introduction of a capacitor-based isolation barrier into the Cockcroft-Walton converter to support isolated power transfer in applications requiring extreme conversion ratios. The proposed topology, shown in Fig. 2, relies on distributed

Fig. 1: Example system diagram for a partial power processing converter.

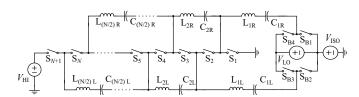

inductors to achieve full soft charging, and uses capacitors to create an isolation barrier between the converter's input and output return path. For this topology, the level count is equal to the conversion ratio. This work presents the design, analysis, and characterization of a 6:1 capacitively-isolated Cockcroft-Walton prototype, with hardware results validated at a high-side voltage of 120 V and a demonstrated 60 V of isolation.

Fig. 2: Schematic of an N-level capacitively-isolated Cockcroft-Walton converter.

### II. ANALYSIS

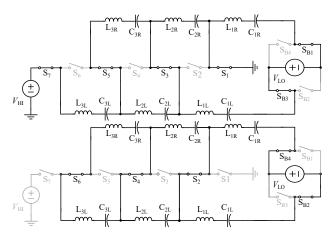

Figure 3 shows the two-phase operation of a 6:1 variant of the proposed topology. An odd level count introduces significant changes to analysis and design of the converter and will not be presented in this work. However, analysis presented holds for any even level conversion ratio. Charge flow analysis [11] of the 6:1 converter yields a normalized charge vector of (1) for capacitor vector (2).

$$q = [3, 3, 2, 2, 1, 1] \tag{1}$$

$$C = [C_{1L}, C_{1R}, C_{2L}, C_{2R}, C_{3L}, C_{3R}]$$

(2)

© 2025 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

DOI: 10.1109/APEC48143.2025.10977355

Fig. 3: (a) Phase one operation of a 6:1 isolated Cockcroft-Walton converter under two-phase control. (b) Phase two operation.

The charge at each stage can be generalized for an N-level version of the converter as (3) where k is the index of the left and right capacitors as defined in Fig. 2. The peak-to-peak capacitor ripple for both capacitors in stage k is defined as (4).

$$q_k = \frac{N}{2} - k + 1 \tag{3}$$

$$\Delta v_{pp,k} = \frac{q_k}{C_k} \tag{4}$$

Equal capacitor ripple is chosen to simplify analysis of the converter. Therefore, flying capacitor values are calculated as (5), where each value is scaled by the capacitance at the  $\frac{N}{2}$  stage,  $C_0$ . The resultant capacitor vector normalized by  $C_0$  for this 6:1 converter is then (6).

$$C_k = C_0(\frac{N}{2} - k + 1) \tag{5}$$

$$C = [1, 1, 2, 2, 3, 3] \tag{6}$$

Accordingly, inductors in each stage are selected to maintain resonant operation. The resonant frequency is presented in (7), where  $L_0$  and  $C_0$  are the values of the inductors and capacitors, respectively, at stage  $\frac{N}{2}$  of the converter. As a result, the inductor value at each stage is equal to (8).

$$f_{res} = \frac{1}{2\pi\sqrt{L_0C_0}}\tag{7}$$

$$L_k = \frac{L_0}{\frac{N}{2} - k + 1} \tag{8}$$

The inductor vector for this converter, normalized by  $L_0$ , is as follows.

$$L = [1, 1, \frac{1}{2}, \frac{1}{2}, \frac{1}{3}, \frac{1}{3}] \tag{9}$$

The mid-range capacitor voltages can be generalized to the following, where the isolation voltage,  $V_{\rm ISO}$ , is defined as the dc voltage offset between the low side of the rectifier and the input ground.

$$v_{k,L} = \begin{cases} -V_{\text{ISO}} & \text{for } k = 1\\ \frac{2V_{\text{HI}}}{N} & \text{for } k = [2, \frac{N}{2} - 1] \end{cases}$$

(10)

$$v_{k,R} = \begin{cases} \frac{V_{\text{HI}}}{N} - V_{\text{ISO}} & \text{for } k = 1\\ \frac{2V_{\text{HI}}}{N} & \text{for } k = [2, \frac{N}{2} - 1] \end{cases}$$

(11)

The switch voltages are presented in (12), where m is the index of the switch as described in Fig. 2. Note, the switch stress decreases as a function of level count, enabling the usage of lower voltage switches, which have improved figures of merit [12] [13] [14]. Moreover, as is typical of resonant tank converters [15], the switch voltage does not experience increased stress with capacitor ripple and can be sized independent of load and isolation voltage.

$$v_{ds,m} = \begin{cases} \frac{V_{\text{HI}}}{N} & \text{for } m = [1, N+1] \\ \frac{2V_{\text{HI}}}{N} & \text{for } m = [2...N] \\ \frac{V_{\text{HI}}}{N} & \text{for } m = B[1-4] \end{cases}$$

(12)

Fig. 4: Passive volume as a function of level count and isolation voltage.

Previous work [16] introduces a method for optimizing capacitor and inductor sizing for hybrid switched-capacitor converters operating at and above resonance. This approach computes the peak energy stored in each passive component and then uses the approximate energy density of capacitors and inductors, as found in [17], to determine the total volume of the passive components. Figure 4 shows this method applied to the capacitively-isolated Cockcroft-Walton converter demonstrated in this work. As the level count, conversion ratio, or isolation voltage is increased, the energy storage required of the capacitors also increases, thereby increasing the total

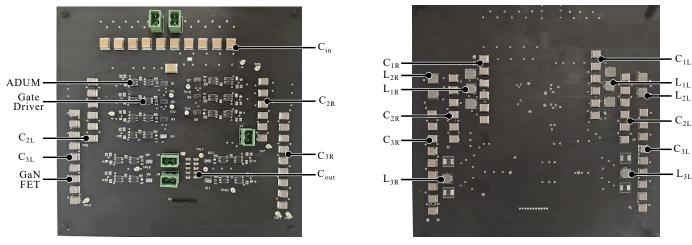

Fig. 5: (a) Front side of the 6:1 Cockcroft-Walton prototype. (b) Back side of the prototype.

passive component volume.

## III. HARDWARE DESIGN

A 6:1 capacitively-isolated resonant Cockcroft-Walton converter was built to validate the proposed topology and analysis. The operating conditions are shown in Table I. The value of  $C_0$  was informed by the optimization method [16] with consideration for level count and conversion ratio, and then selected from among commercially available capacitors of discrete values. The value of  $L_0$  was chosen for resonant operation at 200 kHz, per (7). The passive components are listed in Table II. The prototype board uses a two-sided design for improved space utilization: switching cells and bulk input and output capacitor banks are on the top side of the board as seen in Fig. 5a, while the flying capacitors are on both sides of the board, and the inductors are solely on the bottom side, as in Fig. 5b. To minimize the commutation loop, the string switches were placed in a U-shape, such that  $S_1$  and  $S_7$  (Fig. 3) are close to the input. For the initial experimental prototype, signal and logic power isolation were achieved using ADUM5241s. Future implementations of this topology will investigate using cascaded bootstrap circuits to improve the overall system efficiency and to decrease board area [18]. The distributed inductors can be replaced with a lumped inductor on both input sides of the bridge. This would allow for a reduced passive component volume relative to the version of the converter with distributed inductors, owing to inductor scaling laws as presented in [19]. However, removing the resonant tanks at each stage of the converter will remove the converter's soft charging capabilities, so a converter with lumped inductance under two-phase control would incur hard charging losses. To avoid this, split-phase control can be implemented on the converter.

#### IV. EXPERIMENTAL RESULTS

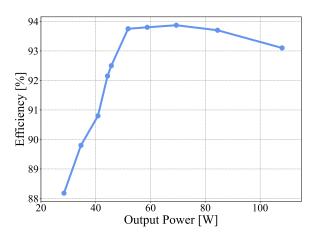

The measured efficiency of the 6:1 converter across various loads at 120 V input voltage and 0 V of isolation voltage is demonstrated in Fig. 6. The converter's peak efficiency was

| Description         | Parameter | Value   |

|---------------------|-----------|---------|

| Output Voltage      | $V_{OUT}$ | 20 V    |

| Input Voltage       | $V_{IN}$  | 120 V   |

| Operating Frequency | $f_{res}$ | 193 kHz |

| Isolation Voltage   | $V_{ISO}$ | 60 V    |

TABLE I: Converter specifications.

Fig. 6: Measured hardware prototype efficiency as a function of output power, with fixed 120 V input.

found to be 93.87% at a load of 5  $\Omega$  and an output power of 69.4 W. The efficiency was measured with a Yokogawa WT5000 power analyzer and does not include gate drive losses.

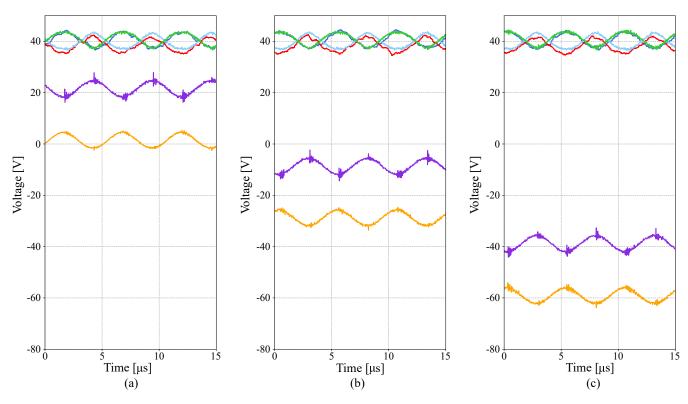

Figure 7 demonstrates the isolation capability of the converter by presenting the measured flying capacitor voltages at a  $V_{ISO}$  of 0 V, 30 V, and 60 V. This figure validates (10) and (11). Furthermore, the sinusoidal nature of the flying capacitor voltages indicates resonant operation, affirming the passive component vectors in (6) and (9) Additionally, the sinusoidal waveforms in Fig. 7 indicate soft charging of the

Fig. 7: (a) Measured flying capacitor voltages with an applied isolation voltage of 0 V, (b) 30 V, and (c) 60 V.

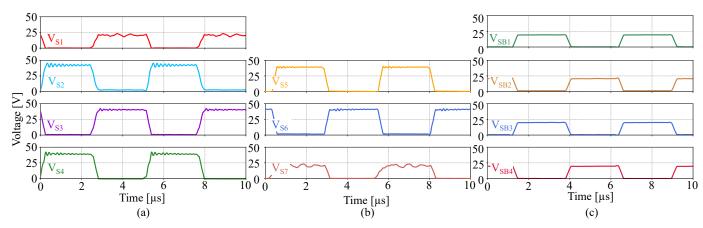

Fig. 8: (a) Switch voltages measured at an input voltage of 120 V.

| Component           | Part Number         | Description         |

|---------------------|---------------------|---------------------|

| $C_0$               | C5750NP02W104J280KA | 100 nF, 450 V       |

| $L_0$               | IHLP2525CZERR33M01  | 330 nF, 20 A        |

| $C_{in}$            | KTS501B105M76N0T00  | $1\mu F$ , 500 V    |

| $C_{out}$           | CL31B105KCHNNNE     | $1\mu F$ , 100 V    |

| $S_{[1-7]/[B1-B4]}$ | EPC2304ENGRT        | 200 V, 5 m $\Omega$ |

| Gate Driver         | NCP81074ADR2G       | 5 V, 10 A           |

| Isolator            | ADUM5241ARZ         | Power and Signal    |

TABLE II: Components for the hardware prototype.

capacitors owing to the inductors distributed at each stage of the converter. The ripple on the flying capacitors is equal in magnitude, further supporting the component scaling vectors. The generalized switch voltage equations presented in (12) are experimentally validated in Fig. 8, where all 11 switching devices are measured at an input voltage of 120 V.

# V. CONCLUSION

This work has presented the analysis, design, and implementation of a 6:1 capacitively-isolated Cockcroft-Walton converter capable of achieving isolation between the input and output return path. Contributions include generalized equations for mid-range flying capacitor voltages for even level counts, as well as generalized switch voltage equations and verification of the topology under various levels of isolation. These

equations are validated in hardware, and experimental results are shared. The prototype converter reaches a peak efficiency of 93.87% at an input voltage of 120 V and output power of 69.4 W, thereby proving the suitability of this converter for future implementation in partial power processing converters.

#### REFERENCES

- Z. Ye, S. R. Sanders, and R. C. N. Pilawa-Podgurski, "Modeling and comparison of passive component volume of hybrid resonant switchedcapacitor converters," *IEEE Transactions on Power Electronics*, vol. 37, no. 9, pp. 10903–10919, 2022.

- [2] P. Granello, F. Pellitteri, R. Miceli, and L. Schirone, "Highly efficient capacitive galvanic isolation for ev charging stations," in 2022 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), pp. 389–394, 2022.

- [3] S. Pourjafar, O. Husev, and C. Roncero-Clemente, "Review and outlook of isolated capacitive coupling based converters," in 2024 IEEE 18th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), pp. 1–6, 2024.

- [4] J. Baek, Y. Elasser, K. Radhakrishnan, H. Gan, J. P. Douglas, H. K. Krishnamurthy, X. Li, S. Jiang, C. R. Sullivan, and M. Chen, "Vertical stacked lego-pol cpu voltage regulator," *IEEE Transactions on Power Electronics*, vol. 37, no. 6, pp. 6305–6322, 2022.

- Electronics, vol. 37, no. 6, pp. 6305–6322, 2022.

[5] M. H. Ahmed, C. Fei, F. C. Lee, and Q. Li, "Single-stage high-efficiency 48/1 v sigma converter with integrated magnetics," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 1, pp. 192–202, 2020.

- [6] C. Li, Y. E. Bouvier, A. Berrios, P. Alou, J. A. Oliver, and J. A. Cobos, "Revisiting "partial power architectures" from the "differential power" perspective," in 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), pp. 1–8, 2019.

- [7] J. Dickson, "On-chip high-voltage generation in mnos integrated circuits using an improved voltage multiplier technique," *IEEE Journal of Solid-State Circuits*, vol. 11, no. 3, pp. 374–378, 1976.

- [8] A. Jackson, N. M. Ellis, and R. C. Pilawa-Podgurski, "A capacitivelyisolated dual extended lc-tank hybrid switched-capacitor converter," in 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1279–1283, 2022.

- [9] S. Coday, E. Krause, M. E. Blackwell, N. M. Ellis, A. Barchowsky, and R. C. Pilawa-Podgurski, "Design and implementation of a gan-based capacitively-isolated hybrid dickson switched-capacitor dc-dc converter

- for space applications," in 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 3154–3159, 2023.

- [10] L. Müller and J. W. Kimball, "High gain dc-dc converter based on the cockcroft-walton multiplier," *IEEE Transactions on Power Electronics*, vol. 31, no. 9, pp. 6405–6415, 2016.

- [11] M. D. Seeman and S. R. Sanders, "Analysis and optimization of switched-capacitor dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 23, no. 2, pp. 841–851, 2008.

- [12] J. T. Stauth, "Pathways to mm-scale dc-dc converters: Trends, opportunities, and limitations," in 2018 IEEE Custom Integrated Circuits Conference (CICC), pp. 1–8, 2018.

- [13] R. A. Abramson, S. J. Gunter, D. M. Otten, K. K. Afridi, and D. J. Perreault, "Design and evaluation of a reconfigurable stacked active bridge dc/dc converter for efficient wide load-range operation," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 3391–3401, 2017.

- [14] M. Guacci, D. Bortis, and J. W. Kolar, "High-efficiency weight-optimized fault-tolerant modular multi-cell three-phase gan inverter for next generation aerospace applications," in 2018 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 1334–1341, 2018.

- [15] C. Schaef, J. Rentmeister, and J. T. Stauth, "Multimode operation of resonant and hybrid switched-capacitor topologies," *IEEE Transactions* on *Power Electronics*, vol. 33, no. 12, pp. 10512–10523, 2018.

- [16] N. M. Ellis, N. C. Brooks, M. E. Blackwell, R. A. Abramson, S. Coday, and R. C. N. Pilawa-Podgurski, "A general analysis of resonant switched-capacitor converters using peak energy storage and switch stress including ripple," *IEEE Transactions on Power Electronics*, vol. 39, no. 7, pp. 8363–8383, 2024.

- [17] N. C. Brooks, J. Zou, S. Coday, T. Ge, N. M. Ellis, and R. C. N. Pilawa-Podgurski, "On the size and weight of passive components: Scaling trends for high-density power converter designs," *IEEE Transactions on Power Electronics*, vol. 39, no. 7, pp. 8459–8477, 2024.

- Power Electronics, vol. 39, no. 7, pp. 8459–8477, 2024.

[18] Z. Ye, Y. Lei, W. C. Liu, P. S. Shenoy, and R. C. Pilawa-Podgurski, "Improved bootstrap methods for powering floating gate drivers of flying capacitor multilevel converters and hybrid switched-capacitor converters," *IEEE Transactions on Power Electronics*, vol. 35, pp. 5965–5977. June 2020.

- [19] C. R. Sullivan, B. A. Reese, A. L. F. Stein, and P. A. Kyaw, "On size and magnetics: Why small efficient power inductors are rare," in 2016 International Symposium on 3D Power Electronics Integration and Manufacturing (3D-PEIM), pp. 1–23, 2016.